Tuchi_

8 months ago

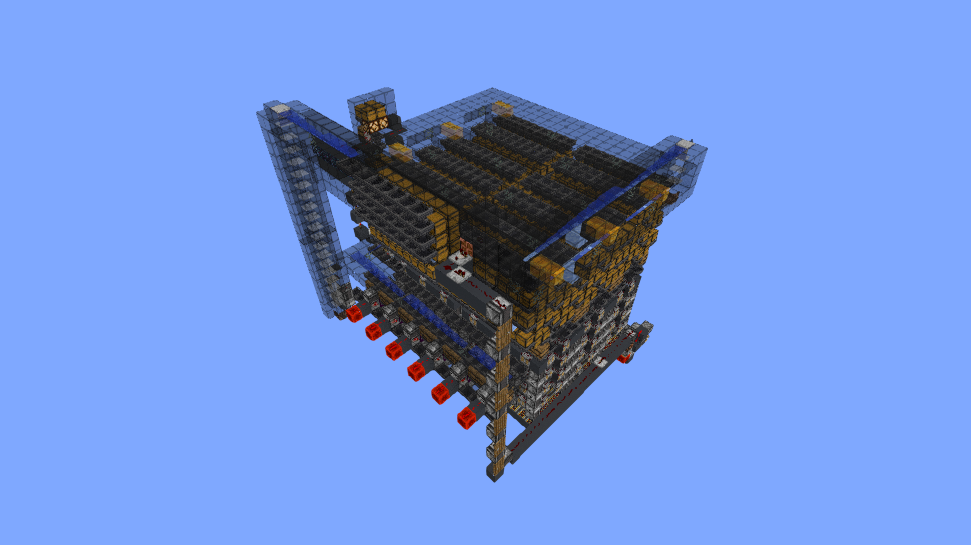

Checks for RAW dependencies between source and destination operands. Each entry holds allows for up to two source operands and one destination operands, with disables available for fine operand control.

5-bit Operands

5 entries

3op, 2op, 1op compatible

(Not a standalone unit, part of issue logic)

0

Blocks

0

Volume

?×?×?

Dimensions

schem

Format

Comments

0

More like this

View all

↵

select

↑↓

navigate

esc

close

5 results

2 plugins loaded