Description

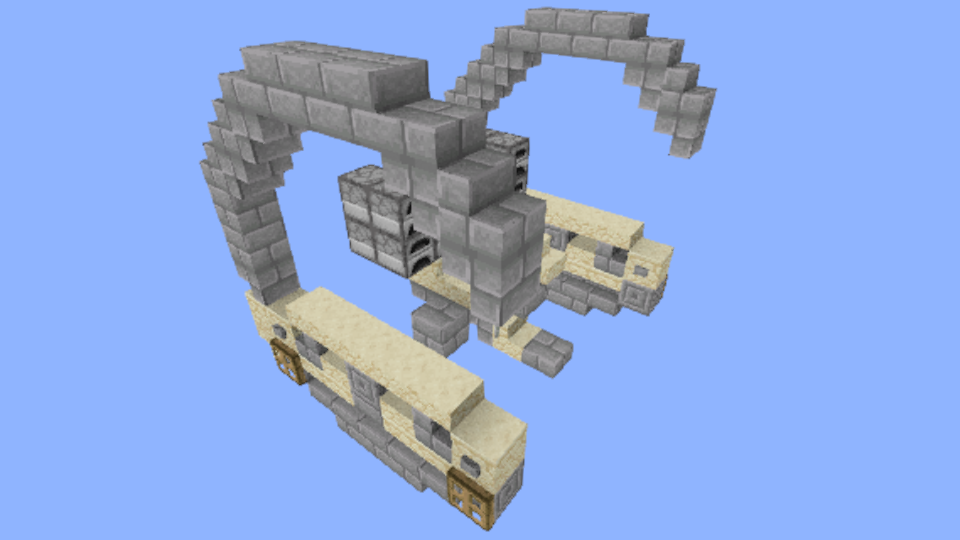

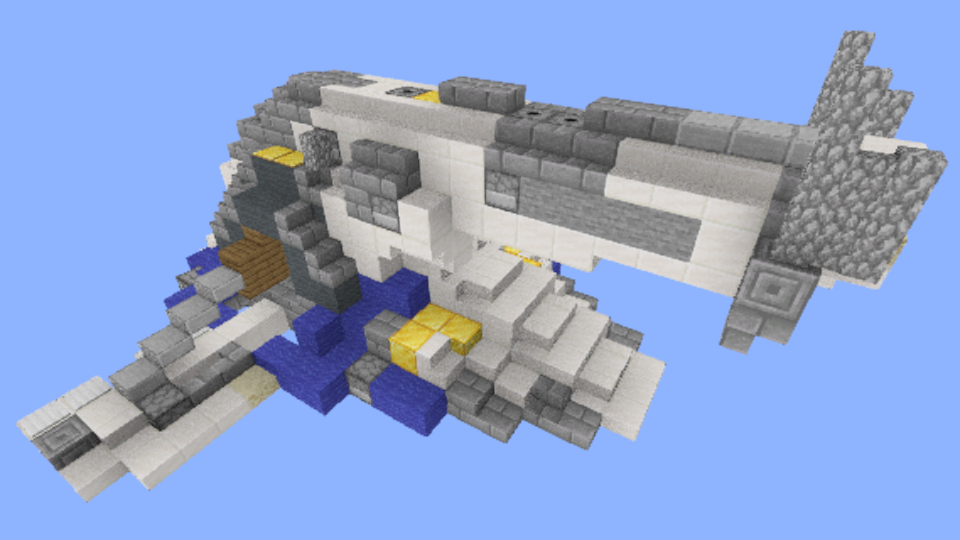

A 32-bit RISC-V processor in Minecraft by StackDoubleFlow.

Related Schematics

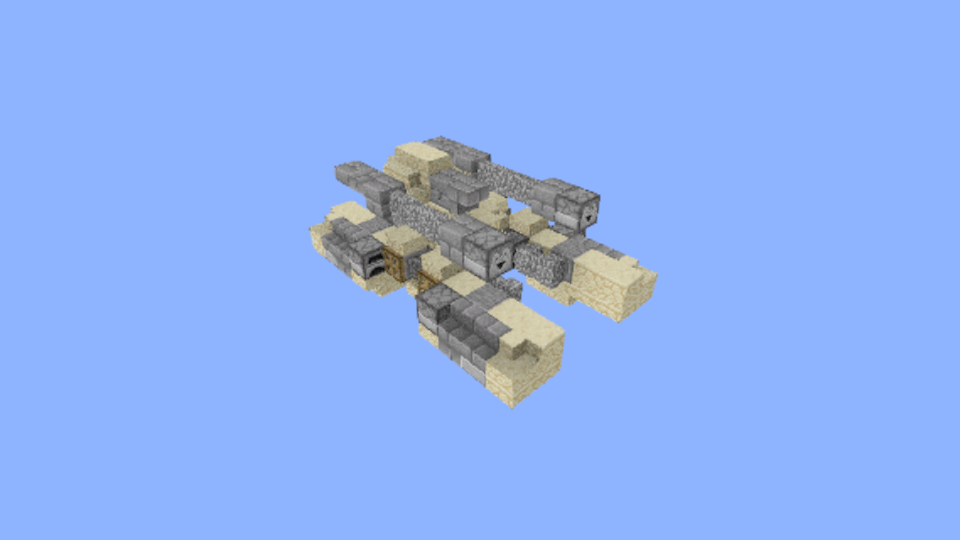

ALU 16bit

16-bit ALU created by jezszymon, based on the 8-bit ALU created by dfgch.

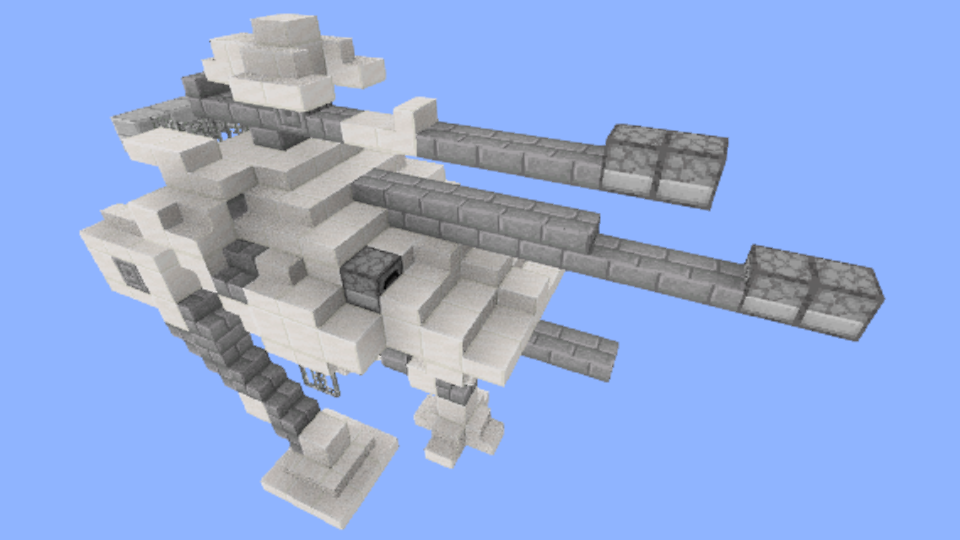

8 bit barrel shifter version A

3 ticks, excluding input/output busleft shift, right shift, arithmetic right shift, rotate. blue: data input, inverted, 15ss required purple: shift amount input, normal, 15ss required.keep in mind that doing a right shift by X is the same as doing a left shift by -X. please input the 2s complement if you want right shifts. yellow: output, normal, low output red: - disable left shift, use when only doing right shift- disable right shift, use when only doing left shift- disable barrelshifter- disable sign extend, for use with arithmetic right shift